Wafer di silicio: difficili da produrre e con alte barriere. Questo articolo descrive il processo di produzione dei wafer, l'analisi dei costi di produzione e le principali barriere.

Il processo di Produzione dei Wafer

La materia prima per i wafer di silicio è il quarzo, comunemente chiamato sabbia, che può essere estratto direttamente in natura. Il processo di fabbricazione dei wafer può essere realizzato in diverse fasi. Disossidazione e purificazione, raffinazione del polisilicio, lingotti monocristallini (barre), burattatura, taglio dei wafer, lucidatura dei wafer, ricottura, test, imballaggio e altre fasi.

Disossidazione e purificazione: La materia prima per gli impianti di produzione di wafer di silicio è il minerale di quarzo, la principale materia prima del minerale di quarzo è il biossido di silicio (SiO2). Il minerale di quarzo viene prima disossigenato e purificato in un processo che include selezione, separazione magnetica, flottazione, degassificazione ad alta temperatura e così via. Le principali impurità del minerale vengono rimosse, come ferro, alluminio e altre impurità. Raffinazione del silicio policristallino: dopo aver ottenuto SiO2 relativamente puro, si effettua una reazione chimica per produrre silicio monocristallino. La reazione principale è SiO2 + CàSi + CO, con monossido di carbonio (CO) come gas, che viene evaporato direttamente dopo il completamento della reazione. Così rimangono solo i cristalli di silicio. A questo punto il silicio è policristallino e grossolano, con alcune impurità come ferro, alluminio, carbonio, boro, fosforo, rame e così via. Per filtrare le impurità in eccesso, il silicio grezzo risultante deve essere lavato con acido, comunemente usando acido cloridrico (HCl), acido solforico (H2SO4), ecc. Il contenuto di silicio dopo l'immersione in acido è generalmente superiore al 99,7%. Durante il processo di decapaggio, ferro, alluminio e altri elementi vengono dissolti nell'acido e filtrati. Tuttavia, il silicio reagisce anche con l'acido per formare SiHCl3 (tricloruro di silicio) o SiCl4 (tetracloruro di silicio). Tuttavia, entrambe queste sostanze sono gassose, quindi dopo il lavaggio acido, le impurità originali come il ferro e l'alluminio sono state dissolte nell'acido, ma il silicio è passato allo stato gassoso. Infine il SiHCl3 o SiCl4 gassoso ad alta purezza viene ridotto con idrogeno per ottenere polisilicio ad alta purezza, SiHCl3+H2àSi+3HCl, SICl4+2H2àSi+4HCl. a questo punto si ottiene il polisilicio da produrre.

CZ (metodo di disegno diretto)

Il metodo straight-draw (CZ) dei wafer di silicio è usato principalmente nella logica, nei chip di memoria e rappresenta circa il 95% del mercato; il metodo straight-draw ha avuto origine nel 1918 quando Czochralski ha estratto filamenti sottili dal metallo fuso, da cui il nome metodo CZ. Questa è la tecnologia dominante per la coltivazione del silicio monocristallino oggi. Il processo principale consiste nel mettere il polisilicio in un crogiolo, riscaldarlo per farlo fondere, poi bloccare un pezzo di cristallo di silicio a cristallo singolo di seme, sospenderlo sopra il crogiolo e tirarlo dritto, con un'estremità inserita nella fusione fino a fondere, poi ruotarlo lentamente e sollevarlo verso l'alto. In questo modo un singolo cristallo si forma all'interfaccia del liquido e del solido per condensazione graduale. Poiché l'intero processo può essere visto come una replica dei cristalli del seme, i cristalli di silicio risultanti sono cristalli di silicio a cristallo singolo. Inoltre, il drogaggio dei wafer viene effettuato anche durante il processo di estrazione del cristallo singolo, di solito sia in fase liquida che in fase gassosa. Il drogaggio in fase liquida significa che il crogiolo è drogato con elementi di tipo P o N, che possono essere tirati direttamente nelle barre di silicio durante il processo di estrazione del cristallo singolo. Laminazione del diametro: poiché è difficile controllare il diametro delle aste di silicio a cristallo singolo durante il processo di trazione del cristallo singolo, al fine di ottenere diametri standard come 6", 8", 12", ecc, le aste di silicio vengono laminate e macinate. Dopo aver estratto un singolo cristallo, il diametro del lingotto viene laminato e rettificato, ottenendo una superficie liscia e un errore dimensionale minore. Taglio e smussatura: Una volta ottenuti i lingotti, i wafer vengono tagliati. I lingotti vengono posti su una macchina da taglio fissa e tagliati secondo il programma di taglio che è stato impostato. A causa del piccolo spessore dei wafer di silicio, i bordi dei wafer tagliati sono molto taglienti. Lo scopo della smussatura è di creare un bordo liscio. Il wafer smussato ha uno stress centrale inferiore, rendendolo così più forte e meno incline alla frammentazione nella successiva fabbricazione del chip. Lucidatura: Lo scopo principale della lucidatura è quello di rendere la superficie del wafer più liscia, piatta e priva di danni e di assicurare uno spessore costante da wafer a wafer. Test e imballaggio: dopo aver ottenuto i wafer lucidati, le proprietà elettriche dei wafer devono essere testate, come la resistività e altri parametri. La maggior parte delle fabbriche di wafer ha un servizio di wafer epitassiali, e se sono richiesti wafer epitassiali, allora viene effettuata la crescita epitassiale del wafer. Se i wafer epitassiali non sono richiesti, vengono imballati e spediti ad altre fabbriche di wafer epitassiali o di wafer.

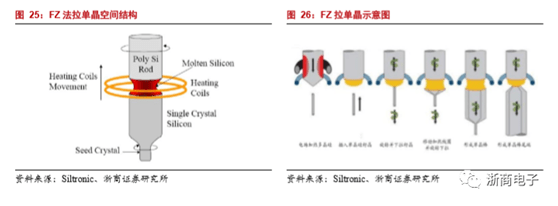

FZ (Zonizzazione frazionata)

I wafer di silicio a fusione di zona (FZ) sono usati principalmente in alcuni chip di potenza, con una quota di mercato di circa il 4%; i wafer di silicio fatti con FZ (fusione di zona) sono usati principalmente per dispositivi di potenza. Le dimensioni dei wafer sono principalmente 8" e 6", e attualmente circa il 15% dei wafer sono realizzati con il metodo FZ. Rispetto ai wafer fatti con il metodo CZ, il metodo FZ è caratterizzato da una resistività relativamente alta, da una purezza più elevata e da una resistenza all'alta tensione, ma è più difficile fare wafer grandi e ha scarse proprietà meccaniche, quindi è spesso usato per wafer di dispositivi di potenza e meno spesso per circuiti integrati.

Il metodo di fusione a zone per fare barre di silicio a cristallo singolo è un totale di tre fasi: riscaldamento del polisilicio, contatto del cristallo di seme e trazione del cristallo singolo mediante rotazione verso il basso. In una camera di forno sotto vuoto o gas inerte, un campo elettrico viene utilizzato per riscaldare le barre di polisilicio fino a quando il polisilicio nella zona riscaldata si fonde, formando una zona fusa. La zona fusa viene poi toccata con cristalli di semi e fusa. Infine, la zona fusa sul polisilicio viene continuamente spostata verso l'alto spostando la posizione di riscaldamento del campo elettrico, mentre i cristalli di semi ruotano lentamente e si allungano verso il basso, formando gradualmente barre di silicio a cristallo singolo. Poiché i crogioli non vengono utilizzati nel metodo di fusione a zone, si evitano molte fonti di contaminazione e i singoli cristalli estratti con il metodo di fusione a zone sono caratterizzati dalla loro elevata purezza.

Analisi dei costi di produzione dei wafer

Costi di produzione di wafer di nuova energia

Il costo dei wafer fotovoltaici può essere approssimativamente diviso in costo del silicio, costo dei cristalli lunghi e costo del taglio. Il costo del silicio è la parte che consuma di più, rappresentando circa il 50% del costo totale. La principale differenza di costo tra i wafer monocristallini e policristallini è nel processo a cristalli lunghi, poiché il silicio monocristallino e quello policristallino hanno diversi requisiti per il processo a cristalli lunghi. Nel processo di affettamento, i produttori di wafer possono aumentare la quantità di wafer tagliati per condividere il costo. Attrezzatura, elettricità, gas speciale e costi di manodopera nel processo del cristallo lungo, ecc.

Costi di produzione monocristallini: in termini di costi del silicio e di taglio, la differenza tra silicio monocristallino e policristallino non è significativa. Il segmento dei cristalli lunghi è la principale differenza di costo. Per quanto riguarda la struttura dei costi dei wafer di silicio monocristallino, il costo del materiale di silicio rappresenta circa il 50%, il costo di estrazione delle barre di silicio monocristallino rappresenta circa il 33% del costo complessivo e il costo del taglio rappresenta circa il 17%. Il costo del crogiolo e l'elettricità sono le principali fonti di costo nella struttura dei costi del processo di estrazione del monocristallo, con entrambi che rappresentano un totale di circa il 45%. I costi rimanenti sono dominati dal campo caldo di grafite e dai costi di ammortamento. In termini di costi del crogiolo, il crogiolo di quarzo usato per l'estrazione del cristallo singolo può incrinarsi o rompersi dopo le alte temperature, il raffreddamento, ecc. Inoltre, poiché la pulizia del crogiolo è molto alta per il tiro a cristallo singolo, la pulizia del crogiolo usato non può essere garantita e la qualità del crogiolo è alta per il silicio a cristallo singolo. Pertanto, i crogioli per l'estrazione del cristallo singolo sono più costosi e non possono essere riutilizzati. Per quanto riguarda i costi dell'elettricità, i produttori nazionali di wafer per semiconduttori o di wafer fotovoltaici stanno costruendo impianti nella Mongolia interna, Yunnan, Guizhou e altre regioni dove i costi dell'elettricità sono relativamente bassi, il che aiuta a ridurre i costi. La riduzione dei costi dei wafer di silicio monocristallino proviene da tre fonti principali. In primo luogo, l'aumento della produzione di forni singoli ha assottigliato i materiali di consumo usa e getta come i crogioli e l'ammortamento delle attrezzature. In secondo luogo, costi di elettricità più bassi. In terzo luogo, il vantaggio di prezzo dell'acquisto in massa di silicio.

Costi di fabbricazione del polisilicio: il processo di fabbricazione del polisilicio non richiede l'estrazione di cristalli singoli, quindi il costo dei cristalli lunghi è relativamente basso. Il costo dei cristalli lunghi rappresenta solo il 12% del costo totale. La principale fonte di costo è il costo del silicio, che rappresenta circa il 52% del costo totale. Questo è seguito dal taglio dei costi, che rappresenta circa il 29% dei costi totali. Il campo caldo della grafite rappresenta la quota più alta dei costi dei cristalli lunghi del polisilicio con il 28%. Seguono i costi del crogiolo, dell'ammortamento e dell'elettricità con 16,7%, 16,7% e 13,9% rispettivamente. Poiché i wafer di silicio policristallino sono utilizzati principalmente nei prodotti fotovoltaici e hanno la tendenza ad essere gradualmente sostituiti dai wafer di silicio monocristallino, c'è poco spazio per il calo del costo dei wafer di silicio policristallino.

Costi di produzione dei wafer per semiconduttori

Il costo dei wafer per semiconduttori è più complesso: i wafer per semiconduttori hanno requisiti più elevati in termini di purezza e caratteristiche elettriche rispetto ai wafer per la nuova energia, quindi sono necessari più passaggi di purificazione e fornitura di materie prime nel processo di produzione, con il risultato di una gamma più varia di materiali di produzione. Questo si traduce in una maggiore varietà di materie prime per la fabbricazione, per cui la proporzione dei costi del silicio è relativamente più bassa, ma la proporzione dei costi di fabbricazione è relativamente più alta. Nel frattempo, rispetto al costo dei wafer di silicio della nuova energia, i wafer di silicio per semiconduttori in materiali diretti sono la componente principale dei costi operativi: per i wafer di silicio per semiconduttori, i costi delle materie prime sono il costo principale, rappresentando circa il 47% dei principali costi operativi. Seguono i costi di produzione, che rappresentano circa il 38,6%. Come l'industria dei semiconduttori, l'industria dei wafer di silicio è un'industria ad alta intensità di capitale con un'elevata richiesta di investimenti in attività fisse, che genererà costi di produzione più elevati a causa dell'ammortamento delle attività fisse come macchinari e attrezzature. Infine, ci sono i costi diretti del lavoro, che rappresentano circa il 14,4%. Il polisilicio è la principale componente di costo delle materie prime: Tra i costi delle materie prime per la produzione di wafer di silicio, il polisilicio è la principale materia prima, che rappresenta circa il 30,7%. Seguono i materiali di imballaggio, che rappresentano circa il 17,0%. Poiché i wafer di semiconduttori hanno alti requisiti di pulizia e vuoto, specialmente per i wafer di silicio, che sono altamente suscettibili all'ossidazione, i requisiti per l'imballaggio sono molto più alti di quelli per i wafer di nuova energia. Pertanto, i materiali di imballaggio rappresentano una percentuale maggiore della componente di costo. I crogioli di quarzo rappresentano circa l'8,7% del costo della materia prima. Anche il crogiolo di quarzo utilizzato nella fabbricazione di wafer per semiconduttori è un crogiolo monouso, ma le proprietà fisiche e termiche del crogiolo sono molto più esigenti. I liquidi di lucidatura, le mole e i tamponi rappresentano un totale del 13,8% e sono usati principalmente nel processo di lucidatura dei wafer di silicio. Le utenze rappresentano circa il 15% dei costi di produzione: Il costo totale delle utenze rappresenta circa il 15% dei costi di produzione complessivi, con l'elettricità che rappresenta circa l'11,4% e l'acqua che rappresenta circa il 3,4% dei costi di produzione totali. In termini di importi corrispondenti, il costo totale dell'elettricità e dell'acqua è paragonabile al costo dei materiali di imballaggio e rappresenta circa la metà del materiale di polisilicio, secondo i dati finanziari 2018 di Silicon Industries Group. I costi dell'elettricità sono leggermente più alti dei crogioli di quarzo di circa il 20%.

Principali barriere alla produzione di wafer

Le barriere ai wafer di silicio sono alte, specialmente per i wafer di semiconduttori, e ci sono quattro barriere principali: barriere tecniche, barriere di certificazione, barriere di attrezzature e barriere finanziarie. Barriere tecniche: Le specifiche tecniche dei wafer di silicio sono relativamente grandi, escludendo la dimensione comune, lo spessore dei wafer lucidati, ecc., così come la deformazione, la resistività, la curvatura, ecc. del wafer. Nei wafer da 300 mm, il processo avanzato richiede una maggiore uniformità dei wafer, quindi rispetto ai wafer da 200 mm, la planarità, la deformazione, la curvatura, il residuo metallico superficiale e altri parametri sono aggiunti per monitorare i requisiti di qualità dei wafer da 300 mm. In termini di purezza, i wafer di processo avanzato richiedono circa 9N (99.999999999%) - 11N (99.999999999%), che è la principale barriera tecnica per i fornitori di wafer. I wafer di silicio sono prodotti altamente personalizzati; la purezza è il parametro fondamentale dei wafer di silicio ed è la principale barriera tecnica. Inoltre, i wafer di silicio non sono un prodotto universale e non possono essere replicati. I grandi wafer di silicio hanno specifiche completamente diverse da una fonderia all'altra, e le diverse applicazioni di ogni prodotto finale possono portare a specifiche completamente diverse per i requisiti dei wafer di silicio. Questo richiede ai produttori di wafer di silicio di progettare e produrre diversi wafer per diversi prodotti dei clienti finali, il che rende la fornitura di wafer di silicio ancora più difficile. Barriere di certificazione: i produttori di chip hanno requisiti rigorosi per la qualità delle varie materie prime e sono molto attenti nella selezione dei fornitori. Ci sono alte barriere all'entrata negli elenchi dei fornitori dei produttori di chip. Di solito, i produttori di chip richiedono ai fornitori di wafer di silicio di fornire alcuni wafer per la produzione di prova, e la maggior parte di essi sono utilizzati per i wafer di prova piuttosto che per i wafer di produzione di massa. Dopo aver superato i wafer di prova, produrranno piccoli lotti di wafer per la produzione di massa su una base di prova. Dopo aver superato la certificazione interna, il produttore di chip invierà i prodotti ai suoi clienti a valle e otterrà la loro certificazione del cliente prima della certificazione finale del fornitore di silicio e infine firmando un contratto di approvvigionamento. Ci vuole molto tempo perché i prodotti di un'azienda di wafer per semiconduttori entrino nella catena di approvvigionamento del produttore di chip, e il periodo minimo di certificazione per i nuovi fornitori è di 12-18 mesi. Inoltre, la barriera di certificazione dai wafer di prova ai wafer di produzione di massa: attualmente, la maggior parte dei wafer domestici da 12 pollici rimane nella fornitura di wafer di prova, ma le procedure di certificazione per i wafer di prova e i wafer di produzione di massa sono completamente diverse, e le norme di certificazione per i wafer di produzione di massa sono più severe. I wafer di prova devono essere certificati solo dalla fonderia stessa, dato che non producono chip, e devono essere certificati solo nel sito di produzione attuale. Per i wafer di produzione di massa, tuttavia, devono essere certificati dal cliente finale fabless e monitorati in tutte le fasi del processo di produzione prima che possano essere forniti in volume. In generale, per mantenere una fornitura stabile di silicio e la resa dei chip. Una volta che un produttore di wafer e un fornitore di silicio hanno stabilito una relazione di fornitura, non cambiano facilmente fornitore, ed entrambe le parti stabiliscono meccanismi di feedback per soddisfare le esigenze individuali, e l'adesione tra fornitore di silicio e cliente continua a crescere. I nuovi produttori di wafer che si uniscono alla schiera dei fornitori devono offrire una relazione più stretta e wafer di qualità superiore rispetto ai fornitori originali. Pertanto, nell'industria dei wafer di silicio, l'adesione tra i fornitori di wafer di silicio e i produttori di wafer è maggiore, ed è più difficile per i nuovi fornitori rompere l'adesione. Barriere di attrezzature: L'attrezzatura principale per la produzione di wafer di silicio è il forno monocristallino, che può essere descritto come la "macchina litografica" nei wafer di silicio. I forni monocristallini dei principali produttori internazionali di wafer di silicio sono tutti prodotti da loro stessi. Per esempio, i forni monocristallini di Shin-Etsu e SUMCO sono progettati e prodotti indipendentemente dalla società o attraverso la sua holding, e non possono essere acquistati da altri produttori di wafer. Altri grandi produttori di wafer hanno i loro fornitori indipendenti di forni monocristallini e firmano accordi di riservatezza rigorosi, con il risultato che i produttori di wafer esterni non possono acquistare o possono acquistare solo forni monocristallini comuni, mentre per i forni monocristallini ad alta specifica non possono essere forniti. Quindi la barriera dell'attrezzatura è anche la ragione per cui i produttori nazionali non possono entrare nei fornitori principali di wafer di silicio globali. Barriere finanziarie: I processi di produzione di wafer per semiconduttori sono complessi e richiedono l'acquisto di attrezzature di produzione avanzate e costose, che devono anche essere costantemente modificate e messe a punto in base alle diverse esigenze dei clienti. A causa degli alti costi fissi come l'ammortamento delle attrezzature, i cambiamenti nella domanda a valle hanno un impatto maggiore sull'utilizzo della capacità delle aziende di wafer di silicio, e quindi sui profitti delle aziende di produzione di wafer di silicio. In particolare, le aziende nuove nell'industria dei wafer sono state in perdita quasi fino a quando non hanno raggiunto le spedizioni di scala, richiedendo alte barriere di capitale. Inoltre, poiché le fabbriche hanno un lungo ciclo di certificazione per i wafer di silicio, questo periodo richiede un investimento continuo da parte dei produttori di wafer di silicio, che richiede anche una grande quantità di capitale.